日本電信電話(NTT)と東京大学、理化学研究所、九州大学、科学技術振興機構(JST)は、従来からのコンピュータと同様のロードストア型計算機の考え方や構成を量子コンピュータに適用したアーキテクチャを2025年3月4日に発表した。

この技術は、プログラムの高い移植性(他の環境への移行のしやすさ)と、高効率な量子ハードウェアの活用を可能とするもの。有用な量子計算の早期実現を加速することが期待できる。

この成果は、2025年3月1日から開催されている「The 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA2025)」で発表される。

東京大学大学院理学系研究科の小堀拓生大学院生(当時日本電信電話インターン生)と藤堂眞治教授

日本電信電話株式会社の鈴木泰成研究員と徳永裕己研究員

理化学研究所 量子コンピュータ研究センターの上野洋典基礎科学特別研究員

九州大学大学院システム情報科学研究院の谷本輝夫准教授ら

発表のポイント

■「コピーできない」という量子力学の制約のもとでメモリとプロセッサの役割を再定義し、汎用性と移植性に優れたロードストア型誤り耐性量子コンピュータの設計を新たに提案。

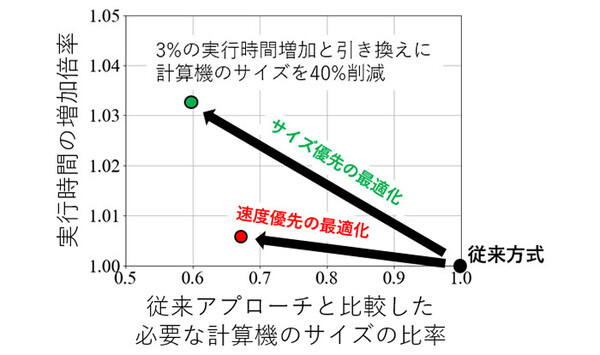

■実用的な量子計算において、従来の量子コンピュータと比較して計算時間の増加を約3%に軽減しつつ、必要なハードウェアの規模を約40%削減できることを示した。

■本成果は発展の初期段階である量子計算機アーキテクチャ研究や、量子誤り耐性計算機の早期実用化に向けた開発に貢献すると期待される。

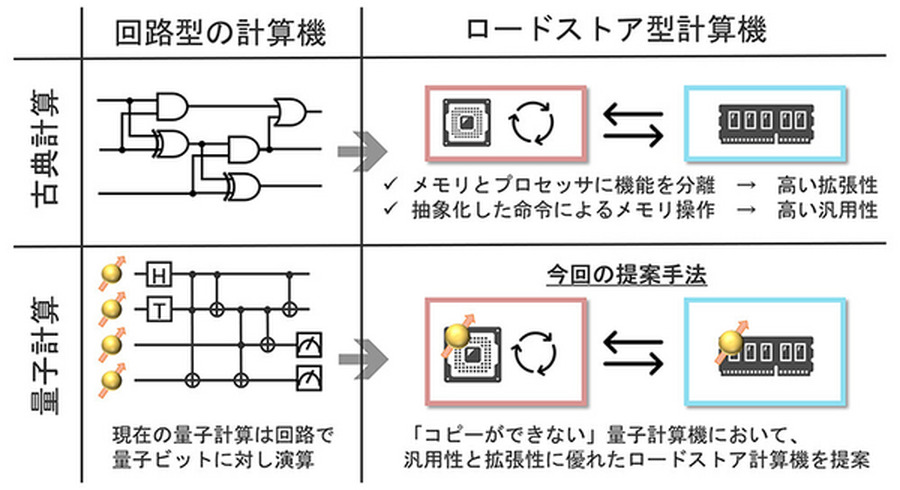

量子コンピュータ「量子回路型」の課題

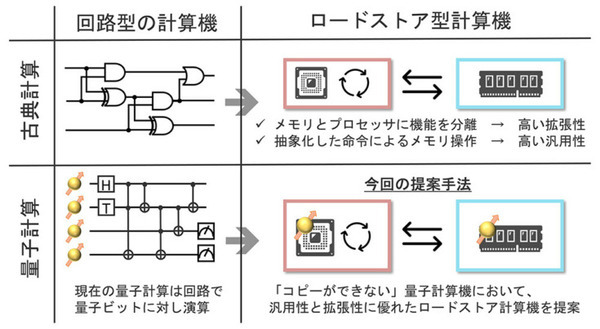

従来の量子コンピュータは「量子回路型」と呼ばれる方式で設計されてきた。この方式は全ての量子的なデータが計算可能なレジスタ領域(記憶装置)に保持され、プログラムは量子回路と呼ばれる論理回路のような形式で表現されて実行されている。

この方式は直感的に理解しやすいなどの利点はあるものの、コンピュータ自体のサイズが大きくなってしまうという課題があった。デバイスのどの場所にデータを保存していても任意の基本演算を可能にしつつ、計算機を拡張する必要があるためだ。

また、この方式の計算機では、プログラムが計算機を構成するデバイスのサイズや誤り訂正方式に特化して最適化されるため、計算機の設計が少しでも変化すると、実行ファイルの計算機間での移植が困難になる。移植性や拡張性にも課題があった。

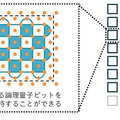

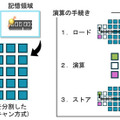

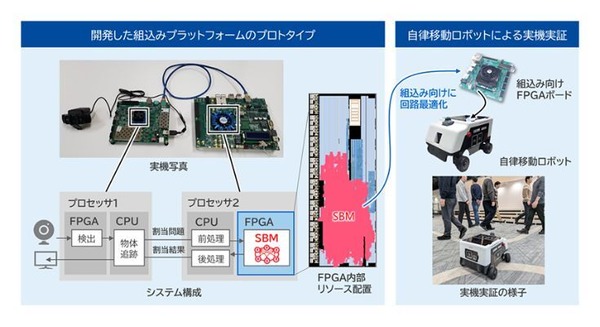

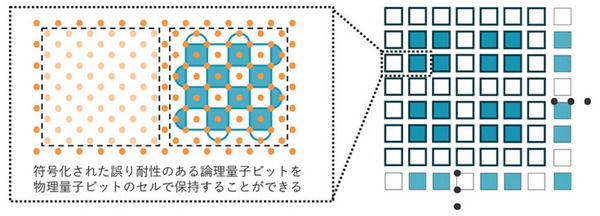

例えば、誤り耐性量子計算として主流な方式である二次元的に並べられた量子ビットを用いて計算を行う方式では、図1のように表面符号と呼ばれる「量子誤り訂正符号」(誤り耐性量子計算のためにエラーを検出、修正するための技術)で符号化されたブロックをデータの単位として計算を行う。

図左:橙丸は物理的な量子ビットであり、一つのセルは通常数百程度の量子ビットによって構成される。図は表面符号での実装例で、白や青色の半円や矩形はエラーの検査パターンを表す。

図右:青色セルが論理的な量子ビット、白色セルがその演算のために割り当てられた補助的なセルを表現している。ここではメモリ効率を青色セル数の全セル数に対する割合で測る。図の設計指針のメモリ効率は44%である。

この際、量子回路型の演算方式に基づいて、全ての符号ブロックで任意の計算を行えるようにするには、データを保持するセル(図1の青色セル)ごとに計算を補助するための追加の符号ブロック(白色セル)を隣接させる必要がある。

この補助的なセルはデータ保持に用いることができないため、量子計算機のハードウェア資源のうち、実際にメモリに利用される割合は典型的には44%、高いものでも67%が限界だった。この実効的なメモリ利用率の低さは、デバイスの大規模化が技術的に困難な量子計算機の開発における主要な障害のひとつとされている。

量子コンピュータに「ロードストア型」を提案

研究グループは、メモリ利用率の低さや移植性の低さといった現代の量子コンピュータが抱える問題を解決する「ロードストア型の量子計算機アーキテクチャ」を提案した。

ロードストア型のアーキテクチャとは、計算機をメモリとプロセッサに分けてデータをやり取りしながら計算を行う方式で、現代のコンピュータで標準的に用いられているアーキテクチャのコンセプトと同様のもの。

この方式ではデータの移動は「ロード」と「ストア」という二つの抽象化された命令でやり取りされるため、具体的なプロセッサやメモリのデバイス構造に依存しない移植性の高い形でプログラムを構築できるメリットがある。

また、メモリはデータを保持する機能しか要求されないため高いメモリ利用率を実現することができる。

この研究では東京大学と日本電信電話株式会社(NTT)がロードストア型のアーキテクチャを導入する枠組みの提案と性能の数値的な評価を、九州大学と理化学研究所が計算機システムとしてロードストア型の機能や命令セットの整備と評価手法の緻密化を担当する形で共同研究を行なった。

量子ハードウェアの資源を大幅に削減

従来の計算機で用いられてきた「ロードストア型のアーキテクチャ」の設計思想を導入することで、量子計算に必要な「量子ハードウェアの資源が大幅に削減」できる。

そのため、汎用性と移植性に優れた新たな量子計算機アーキテクチャとなる可能性が高い。

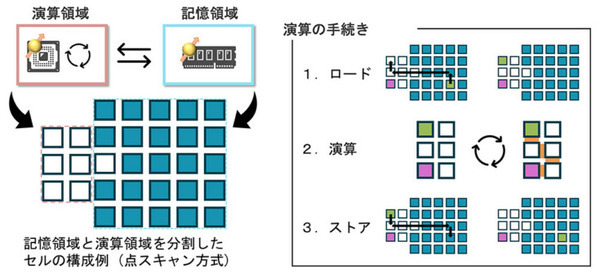

ロードストア型計算機は従来の計算機設計でよく知られている考え方だが、この研究ではこの考え方を量子計算機の特性や制約を踏まえながら、量子計算機の設計に適用することで、図2のように有効な「ロードストア型の量子計算機が構築可能」であることを示した。

図左:本成果で提案した量子メモリ方式によるセル配置の一例。図1の従来設計と比べ、白色セル(演算のために割り当てられた補助的なセル)の割合が低く、青色セル(データを保持するセル)の割合が高くなっており、メモリ効率が高い。左側の白色のセル領域が演算領域、右側の青色セルに占められた領域が記憶領域に相当する。

図右:本成果で提案する演算フロー。この方式ではプログラムは抽象化されたデータの移動と演算のみを指示するため、記憶領域で利用する符号やハードウェアが変化しても実行可能となる。

1.ロード 右側の記憶領域に保持された目的のセル(緑色セル)を所定の論理操作で演算領域に移動する。

2.演算 演算領域にあるセルを補助的なセル(白色セル)や事前にロードされた別のセル(紫色セル)を用いて演算を行う。

3.ストア 演算が完了したセルを記憶領域に戻す。

計算機のサイズを約40%削減

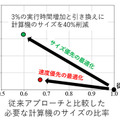

「ロードストア型」の計算に懸念点がないわけではない。これを採用すると、記憶領域と演算領域のメモリ帯域(プロセッサとメモリの間で一定時間に通信可能なデータ量を表す指標のこと)が限られていることによる計算時間の増加が懸念される。

従来の計算機では、プログラムを実行する際にデータのアクセスパターンに偏りが生じる「プログラムが持つメモリアクセスの局所性」を活用したキャッシュ構造や、通信時間を他の演算と被せることで、通信遅延を隠ぺいする仕組みでこうした問題を解決しているという。

この研究では代表的な量子プログラムを量子コンピュータが実行可能な形式に翻訳し、そのメモリアクセスパターンの解析を行うことで、量子計算機でも通常の計算機と同じくメモリアクセスに局所性があることを初めて見いだしました。これを踏まえ、実効的なメモリ通信帯域を改善するキャッシュに類似したテクニックを提案するとともに、通信時間を他の演算操作と被せてアクセス遅延を隠ぺいする機構を構築することで、計算機の全領域で演算が行える計算機と比べた際の計算時間の増加を3%程度まで低減することに成功した(図3)。

従って、ロードストア型量子計算は小さな計算時間の増加で高いメモリ効率と移植性を同時に実現できる優れた設計、だとした。

図は二つの設定で最適化した際の量子計算機の要求性能を表す。

赤色の点:速度優先で最適化した結果。実行時間増加を1%以下に抑えながら計算機のサイズを約30%削減。

緑色の点:サイズ優先で最適化した結果。実行時間の増加は3%になるが、計算機のサイズを約40%削減可能。

今回提案したロードストア型の量子計算アーキテクチャでは、メモリ効率の高い大規模な記憶領域と、メモリ効率は低く小規模だが任意の基本演算が可能な演算領域を組合せて計算を行う。

この際、記憶領域と演算領域間でデータを移動する操作は、ロードとストアという抽象化された命令で統一的に表され、利用する符号やハードウェア設計が変わってもそのまま活用できる高い移植性を実現している。

量子計算でのデータの移動にはクローン禁止定理(任意の量子状態を複製するような量子操作が原理的に不可能であることを示した量子計算の基本的な定理のこと)といった量子情報特有の根本的な性質や、利用する量子デバイスや誤り訂正方式に特有の技術的な制約があるため、効率的に上記のような設計が可能かは明らかではなかった。

新たな量子メモリ方式を提案することで、漸近的には「100%のメモリ効率」が、実用的なケースでも「約90%のメモリ効率」が達成できることを示した。

各氏のコメント

小芦雅斗氏(PM)

大規模な誤り耐性量子コンピュータの実現に向けた理論研究からの貢献の一つは、基礎研究からの積み上げによる、汎用性と拡張性の両面に優れた量子コンピュータのアーキテクチャの提示である。本研究は、現代の従来型コンピュータの仕組みと量子力学の特性や性質を踏まえて量子コンピュータの構成を見つめなおし、量子コンピュータのメモリとプロセッサの機能を再定義することで、そのような優れたアーキテクチャを提案するものである。この成果は目覚ましい発展が続く量子計算の分野において理論と実装のギャップを繋ぐカギとなるものであるとともに、多様な背景を持つ研究者がチームとして取り組むことで得られた本プロジェクトならではの賜物と言える。

山本剛氏(PM)

誤り耐性量子コンピュータの実現方法として、表面符号が現状最も研究開発が進んでいる誤り訂正方式である。しかしながら、この方式では非常に多数の物理量子ビットが必要になるため、量子加速を実現する規模の計算機の実装可能性における大きな課題であった。本研究はこの課題に対して、表面符号が備える理論的性質とコンピュータ設計の知見を活用した量子コンピュータ版のロード・ストア・アーキテクチャを提案することで、量子計算の性能を損なうことなく要求物理量子ビット数を半減させて解決を図るものである。これはムーンショット型研究内プロジェクト間連携による異分野融合の成果であり、大規模誤り耐性量子計算の実現に向けた大きな進展であると言える。

永山翔太氏(PM)

誤り耐性量子コンピュータを早期に実現するにあたり、必要なハードウェア資源量を削減することは極めて重要である。本研究は、表面符号自体やハードウェアへの要求仕様の変更なしに、表面符号の性質をコンピュータ設計の観点から活用し実行時間を大幅に増加させずに量子ビット数を最大で半減させる量子コンピュータ・アーキテクチャを提案するものである。実装を前提とした量子計算のリソース推定における前提を更新する成果であるといえ、大きなインパクトを持つ。多様なバックグラウンドを持つ研究者が集うムーンショット型研究ならではの取り組みであり、さらなる発展的議論が期待される。

発表者・研究者等情報

小堀 拓生 大学院生(当時日本電信電話インターン生)

藤堂 眞治 教授

日本電信電話株式会社

鈴木 泰成 准特別研究員

徳永 裕己 特別研究員

理化学研究所 量子コンピュータ研究センター 超伝導量子計算システム研究ユニット

上野 洋典 基礎科学特別研究員

九州大学大学院システム情報科学研究院

谷本 輝夫 准教授

論文情報

会議名:The 31st IEEE International Symposium on High-Performance Computer Architecture(HPCA2025)

題 名:LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing

著者名:Takumi Kobori*, Yasunari Suzuki*, Yosuke Ueno, Teruo Tanimoto, Synge Todo, Yuuki Tokunaga(*責任著者)