大容量、超低遅延、多数同時接続の「5G」通信インフラ。特に超低遅を活かすには、従来のようにクラウドで行っている処理ではなく、処理の一部を基地局の小規模なデータセンターで行うことで、工場制御、都市交通制御、電力制御など即時に反応が求められる処理を効率的に実現することができる。このようなエッジコンピューティングの方式をMEC(Multi-Access Edge Computing)と呼ぶ。

エッジ領域の高機能化による、個人情報のカプセル化、IoTのローカルな管理、クラウドへの情報輻輳を防ぐ事前処理などによるクラウドとのシームレスな連携や、情報管理が可能になった。このことにより、たとえば病院施設でのAIによる病巣の診断補助、工場施設での生産効率向上のためのセンサデータ解析、スタジアムでの仮想現実(VR)などが考えられる。

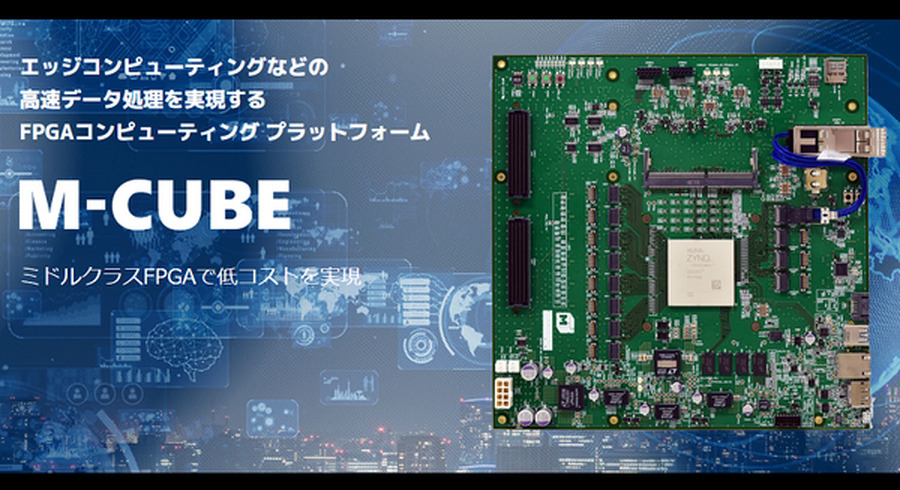

半導体および関連製品販売を手掛ける株式会社PALTEKは、5Gの特長の一つである超低遅延を実現するために不可欠なMECやAIの推論処理などの高速データ処理を実現する、FPGAコンピューティングプラットフォーム M-CUBEの受注を開始。FPGAはfield-programmable gate arrayの略称で、製造後に購入者や設計者が構成を設定できる集積回路のこと。ロボットやドローン、知的な端末等と5Gなどの通信サービスと連携したソリューションも構築できる。

MECは、エッジコンピューティングの規格としてETSI(欧州電気通信標準化機)が標準化を進めているもので、一定エリア内の通信処理の効率化を図る技術だ。MECでは、データをクラウドに送信して処理するのではなく、ユーザーに近い場所(エッジ)でデータの収集と処理を行うため、遅延が減り、広帯域幅アプリケーションを準リアルタイムで実行できる。今後展開されるローカル5Gにおいても、個人情報のカプセル化、IoTによる情報のローカル管理などが可能となる。

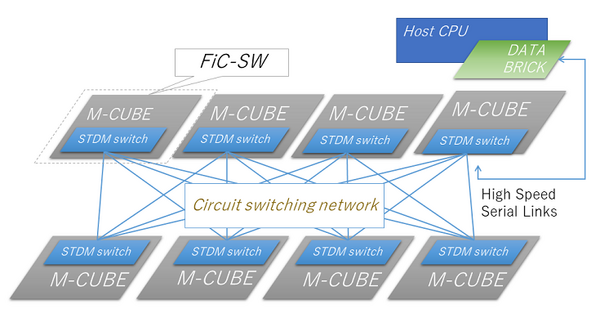

MECの高速処理を可能にするマルチFPGAシステム FiC

現在、FPGAはアルゴリズムをハードウェアで実行する高速計算用加速器(アクセラレータ)として注目されている。慶応義塾大学理工学部教授の天野 英晴氏が中心となって提唱するマルチFPGAシステム FiC(Flow-in Cloud)は、価格性能比に優れた中規模FPGAを高速の双方リンクで複数本接続した大規模計算システムで、全体として巨大な回路を構成することができる。システムの作動中に部分的に再編成を行う機能もあり、柔軟なアプリケーション変更や複数ユーザーによる使用にも対応している。また、回線交換方式をとっているため、ディープラーニングのような同期が必要かつデータサイズが予測できるようなアプリケーションにも適しているシステムで、MECにFiCを活用することでエッジ側での高速処理を実現し、低消費電力で、準リアルタイム処理を行うことが可能となる。

FPGAコンピューティングプラットフォーム M-CUBE

同社が受注・販売するFPGAコンピューティングプラットフォーム M-CUBEは、複数のM-CUBEをつないで、単一のFPGAであるかのように扱うことができるFiCに適合しており、以下の特長により低コストかつ高性能なシステムを実現できる。

M-CUBEの特長

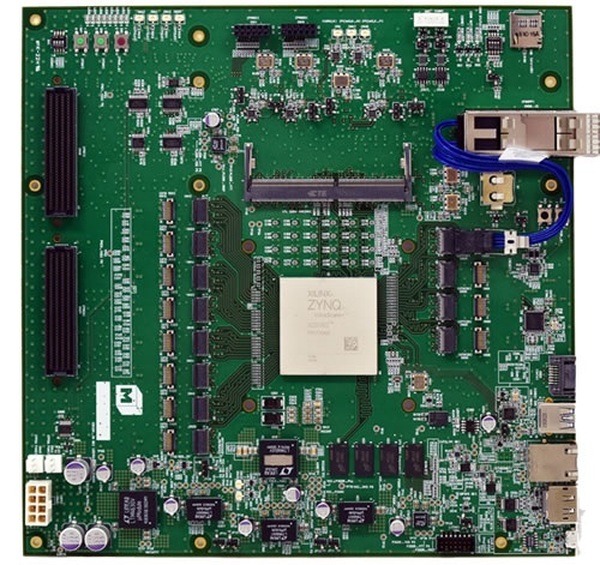

| (1) | 価格性能比に優れたザイリンクス社のSoCである Zynq(R) UltraScale+(TM) MPSoCを搭載(Zynq(R) UltraScale+(TM)シリーズ最大のXCZU19を搭載) |

|---|---|

| (2) | SAMTEC Firefly(TM)ケーブルを使用することで高速双方向リンクが可能となり、超広帯域での基板間通信を実現 |

| (3) | Arm(R)とFPGAの間が広帯域内部バスで接続されているため、システムパフォーマンスが向上 |

関連製品との接続が可能

同プラットフォームを活用することで、エッジコンピューティングの高速化のほか、4K/8Kなどのビデオ処理やスポーツイベント・ライブでの仮想現実/拡張現実(VR/AR)、AIによる病巣の診断補助、工場施設でのセンサデータ解析などのワークロードを高速化でき、システムコストおよび消費電力削減が可能となる。また、同社開発製品である「ImageCUBE 2」や「DATA BRICKとFireFly」で接続することができ、8K映像のデータ処理や8K映像を用いたAIプラットフォームとして活用することもできる。

同プラットフォームについて、天野 英晴教授は以下のようにコメントしている。

慶応義塾大学 情報工学科 教授 工学博士 天野 英晴氏

M-CUBEは、ホストなしでFPGAボード同士を接続して簡単にスケールアップが可能で、C/C++などの高級言語で記述されたアクセラレータモジュールを複数のFPGAボードに簡単に実装できるように工夫されています。低電力かつタイミングクリティカルなジョブにも対応が可能で、将来のMEC(Multi-access Edge Computing)に最適な特徴を持っています。我々が開発したFiCボードに比べて、CPUとFPGAロジックが同一チップ上に組み込まれており、多様なインタフェースを持ち、ボード間の接続リンクも強力になっています。FiCはNEDO委託事業「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/省電力AIエンジンと異種エンジン統合クラウドによる人工知能プラットフォーム」での研究成果を活用したものであり、現在、JST,CREST「MEC用マルチノード統合システムの開発」JPMJCR19K1のテストベットとして研究が進められています。

▼ M-CUBE 製品スペック

| 搭載FPGA | XCZU19EG-2FFG1760 |

|---|---|

| メモリ | PS:4GB DDR4-2400、PL:1x DDR4-2400 SODIMM ソケット |

| ストレージ | SATA(未実装) |

| I/O | QSFP28 (未実装)、4x GTY 4TX/4RX (max 28.125Gbps)、 4x GTH 8TX (max 16.3Gbps)、4x GTH 8TX (max 16.3Gbps)、USB3.0*1、 USB-UART*1、1Gb Ether (RJ45)、DP1.2 |

| 拡張コネクタ | FMCコネクタ*2(LPC,GTはアサインされていない)、PMOD*2 |

| switch/LED | 基板上に搭載 |

| 電源 | ATX |

| 動作時温度 | 0~50℃ |

| 動作時湿度 | 20-80%(結露なきこと) |

| 外形寸法 | MicroATXボードサイズ (243.8mm×243.8mm) |

Image CUBE 2 製品詳細: https://www.paltek.co.jp/cube/ic2/

MDATA BRICKE製品詳細: https://www.paltek.co.jp/designservice/board/databrick/

株式会社PALTEK